Patent MarketPlace: Semiconductor Patents for Sale

Next-Generation Embedded Controllers (Adaptive Computing Machines): Five U.S. Patents and Two U.S. Patent Applications

Next-Generation Embedded Controllers (Adaptive Computing Machines): Five U.S. Patents and Two U.S. Patent Applications

Named after Gordon Moore, the CEO and co-founder of Intel, Moore’s Law states that the power of microchips doubles every two years while the cost is halved. Fulfilling that challenge has become harder and harder in recent years as chipsets get faster and faster, more powerful, and more complex.

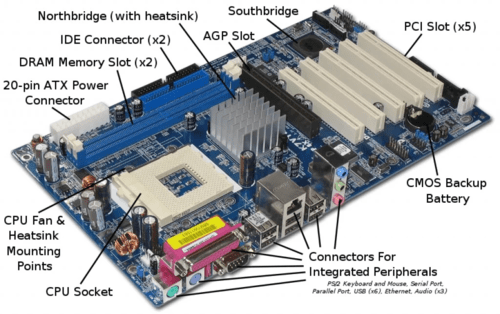

The technology covered by this portfolio takes computing to the next level. The technology starts with a hub board, a common bus, and a plurality of sibling boards. The hub board features an I/O controller hub that includes a main communication chipset, and the sibling boards are coupled to the hub board by the common bus. Each sibling board includes both a memory and a CPU, and a southbridge-type chipset – also known as a “split motherboard design” – that resides in the hub board and is shared among the sibling boards. At least one of the sibling boards functions as a master processing unit for the system, offering processing flexibility based on how they are configured in the system.

This next-generation chipset design enables faster performance at a substantially reduced cost. It will undoubtedly be standard equipment in just a few years in cell phones, computer games, PCs, and most consumer electronics.

Patent Portfolio

- U.S. Patent No. 9,135,203: Computer system and computer device

- U.S. Patent No. 9,471,519: Computer system and computer device

- U.S. Patent No. 9,779,051: Computer system and computer device

- U.S. Patent No. 10,002,097: Computer system and computer device

- U.S. Patent No. 10,620,792: Computing device with an appropriate adaptable user hardware interface

- U.S. Patent Application 20180365187: Computer system and computer device

- U.S. Patent Application 16/845,827: Computing device with an appropriate adaptable user hardware interface

This portfolio will enable any chip designer or manufacturer to leapfrog the technology of all of its competitors. Two Claim Charts for U.S. Patent No. 10,002,097 are available upon request.

Memory Usage Optimization (ADB): International Portfolio

Memory Usage Optimization (ADB): International Portfolio

One of the most challenging components in consumer electronics is the memory. Consumers want more memory, and they want it to be cheaper, more durable, and more versatile. The patents in this eclectic portfolio all address the next-generation of memory, from Class D audio amplifiers to EEPROM to video signals to solid-state memory.

U.S. Patent No. 7,038,534 for a “Class D audio amplifier and method for compensation of power supply voltage influence on output audio signal in class D audio amplifier” enables class D amplifier circuits to smooth out – via filtering – the effect of the supply voltage ripples on the audio output. This provides a more linear or ideal signal amplification function. Claim 5 of the patent is specifically directed toward a method for increasing the quality of an audio signal at the output of a class D audio amplifier through compensation of power supply voltage influence on an output audio signal. This addresses the issue of a low coefficient of rejection of influence of supply voltage fluctuations known as the Power Supply Rejection Ratio (PSRR) coefficient. The novelty of Claim 5 is the method of compensation as a supplement to the electroacoustic amplifier, and the method utilizes various components such as a filter, generator and comparator. This patent would enable any Class D amplifier IC manufacturer to take its products to a new level of performance.

U.S. Patent No. 7,038,534 and European Patent 1702339 for a “Software method of emulation of EEPROM memory” relate to a software emulation of an EEPROM memory that can be used to program another non-volatile memory (NVM) such as a flash memory. It eliminates the need for using an EEPROM, and that saves both cost and circuit board space since flash memories cost much less than EEPROM memories and it is far less expensive to increase the size of the flash memory rather than purchase additional EEPROM. Claims in the patents cover a method for storing an image of an emulated EEPROM in an NVM in two sectors. The first sector stores the emulated EEPROM in part and adds one or more patches to the remaining parts. The image and the changes are then stored in a buffer, and the method then repeats itself until a new patch cannot be added to the first sector. The first and second sector then switch places, store the emulated image from the buffer in the second sector, and erase the first sector. One novelty of this patent is that it involves the application of software emulation of the EEPROM with any currently applied flash memory circuit, and it can emulate any size of currently produced EEPROM circuits up to 64KB. Any manufacturer of NAND and NOR FLASH memory, as well as microprocessor and SoCs producers, would benefit from this patent.

U.S. Patent No. 8,558,876 for a “Method and a system for generating a signal for a video display unit” and European Patent 2429197 for “A method and a system for generating a signal for a video display unit” address generating a video signal for a display unit, be it a two-dimensional (2D) mono video signal or a three-dimensional (3D) stereoscopic video signal. It describes a computer-implemented method for generating an output signal for a display unit in five steps:

- Determining whether a display mode of the display unit is mono or stereoscopic

- Detecting whether the type of video input signal received by the video signal receiver is mono or stereoscopic

- Converting the received video signal into an adapted output signal compatible with the display mode of the display unit

- Providing the adapted output signal to the display unit such as by providing an output test signal to the display unit

- Receiving a display mode identifier from the user.

This patent family will enable any manufacturer of Blu-ray players, STB and 3D TV/Displays to expand the versatility of its products.

U.S. Patent No. 9,015,409 for an “Apparatus and methods for prolonging service life of solid-state memory device in a digital video recorder” covers technology that provides longer service life for solid-state drives (SSDs) by enabling them to withstand a larger number of write cycles in comparison with conventional SSDs. Solid-state drives frequently begin to cause problems when the number of write cycles exceeds 100,0005. Solid-state drive technology has overtaken traditional HDD units as SSDs get cheaper, smaller, lighter and faster – in large part due to the elimination of mechanical parts. To address the growing need for extending the lifetime of DVRs, manufacturers have implemented various techniques to extend the life of SSDs. One of them is “wear-levelling” in which write operations are spread over all available space on the SSD. This patent extends the lifetime of a solid-state disc beyond what the “wear-levelling” technique offers. Traditional DVRs begin a write operation each time the DVR tunes into a channel and displays the audio-video content. This patent instead enables a write operation only when it is detected by the DVR as necessary or only when a user provides a write-triggering command. The SSD includes a detector that sees a functional command from a user, and a controller changes the SSD from a first recording state to a second non-recording state based on each functional user command. The controller repeats the changes between the first state and the second state, and the repetition of these steps lead to extended life for the SSD. The invention covered by this patent makes it possible to avoid large amounts of write cycles of audio-video content which is redundant to the user and just leads to faster wear of the SSD and, consequently, of the DVR. Any manufacturer of solid-state drives or DVRs could use this patent to prolong the lifespan of its products.

Patent Portfolio

- U.S. Patent No. 7,038,534: Class D audio amplifier and method for compensation of power supply voltage influence on output audio signal in class D audio amplifier

- Polish Patent 198380: Electroaciustic amplifier of DC class and method of compensating the influence of supply voltage on useful output signal of such amplifier

- U.S. Patent No. 7,406,558: Software method of emulation of EEPROM memory

- European Patent No. 1702339: Software method of emulation of EEPROM memory

- U.S. Patent No. 8,558,876: Method and a system for generating a signal for a video display unit

- European Patent 2429197: A method and a system for generating a signal for a video display unit

- Eurasian Patent 024564: Method and system for generating a signal for a video display unit

- U.S. Patent No. 9,015,409: Apparatus and methods for prolonging service life of solid-state memory device in a digital video recorder

This portfolio can be acquired as a package on most favorable terms, or selected patents within the portfolio can be acquired based on the needs of the acquiring entity.

Improved Circuit Operations for FinFET Devices (Stephens): Portfolio of Seven U.S. Patents

Improved Circuit Operations for FinFET Devices (Stephens): Portfolio of Seven U.S. Patents

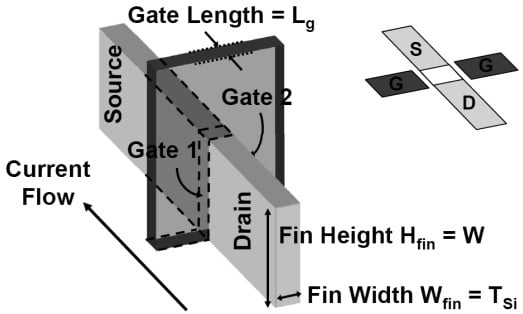

This cutting-edge portfolio covers technology that facilitates and improves the performance of multi-gate FinFET (Fin Field-Effect Transistor) devices. The invention enables calibration or adjustment of the operation of dual-gate transistors such as those used in a sense amplifier or input receiver configuration, overcoming input offset and related issues. Input offset and transistor behavior matching – particularly at lower voltages and with increasingly smaller device geometrics – can cause inconsistent or incorrect circuit operation. This portfolio directly addresses and solves those potential problems!

| Patent No. | Description |

|---|---|

| 9,286,955 | Semiconductor memory device having calibration circuitry for dual-gate transistors associated with a memory array |

| 9,304,525 | Reference level adjustment for calibration of dual-gate transistors |

| 9,344,080 | Dual-gate transistor control based on calibration circuitry |

| 9,455,001 | Semiconductor memory device having calibration circuitry for dual-gate transistors associated with a memory array |

| 9,601,167 | Semiconductor device having dual-gate transistors and calibration circuitry | 9,806,708 | Reference level adjustment for calibration of dual-gate transistors |

| 9,906,218 | Dual-gate transistor control based on calibration circuitry |

The technology covered by this portfolio enables circuits to be tested from each side (its expected output state) to determine calibration results that can significantly reduce or totally eliminate potential matching problems. Current technology can only test one expected output state, and that limits the level of calibration or correction that is possible. This portfolio’s technology is more detailed so it is far more accurate when correcting offset and/or mismatch problems, important factors in today’s higher-performance, smaller-geometry, lower-voltage operations.

This portfolio would be a critical acquisition that would give the acquirer of the portfolio a patent-protected competitive advantage in high performance applications such as SRAM, NAND and flash devices.

High-Speed, Truly Random Number Generator (Scarlett): U.S. Patent No. 9,971,568 and PCT, European, Chinese and Japanese Patent Applications

High-Speed, Truly Random Number Generator (Scarlett): U.S. Patent No. 9,971,568 and PCT, European, Chinese and Japanese Patent Applications

There are random acts of kindness, but there is also a need for randomness for many computer applications – from running simulations to encryption to artificial intelligence (AI) applications. The invention covered by this portfolio uses birefringent splitting, a process that is quantum mechanical in nature and known to be unpredictable. A series of layers take a beam of photons and randomly shuffle the energy so that the output is a random light intensity. Pairing this with a pixel detector produces 250 simultaneous streams of 1-2GHz random data.

This portfolio includes U.S. Patent No. 9,971,568 for the "Generation of random numbers through the use of quantum-optical effects within a mirror cavity system" as well as PCT Patent Application 2016141192, European Patent Application 3265906, Chinese Patent Application 107408033 and Japanese Patent Application 2018513506.

There is currently no device that meets the random data requirements of high-performance computers. The device created by this invention will permit its integration into data centers, or it could be scaled down to a chip-level device that can be incorporated into numerous computing solutions. This portfolio provides an opportunity for high-performance super computer manufacturers, chip manufacturers, fiber optics infrastructure providers and hard drive OEMs to provide an added-value service for its customer base.

Patent Brokerage Prospectus: Contact [email protected] to receive an analysis of each portfolio that includes:

- Executive Summary

- Patent Overview and History

- Technology and Investment Summary

- Market Research

- Company Analysis

- Illustrative Evidence of Use (if applicable)

We offer patents in these technologies:

- Agricultural

- Artificial Intelligence

- Automotive/Vehicular

- Banking/Financial Services

- Beverages/Foods/Nutritional Products

- Boat and Marine

- Cannabis and Medical Marijuana

- Construction/Building Trades

- Consumer Electronics

- Consumer Products

- Digital Currency/Cryptocurrency

- Drones/UAVs

- E-Cigarette & Vaping Technology

- E-Commerce

- Energy/Power Generation

- Health and Beauty Products (HBP)

- IoT Patents/Internet of Things

- Manufacturing

- Medical Electronics and Devices

- Mining/Drilling

- Mobile/Wireless

- Network/Location-Based Services

- Optics/Displays/Video/LED

- OTT Patents/Over-the-Top

- Packaging

- PCs and Notebooks

- Pharmaceuticals

- Robotics/Automation

- Semiconductor

- Smart Home/Smart Office

- Social Media

- Software, Apps, and Architecture

- Sports/Sporting Goods

- Telecommunications/IP Telephony

- Warehousing/Material Handling

- Other

- Go to Patent Index

- Return to Patent MarketPlace